# 2019 GATE

**Graduate Aptitude Test in Engineering**

# GATE 2019

# ANALOG CIRCUITS

**ELECTRONICS ENGINEERING**

### A Unit of ENGINEERS CAREER GROUP

**Head O** ce: S.C.O-121-122-123, 2<sup>nd</sup> oor, Sector-34/A, Chandigarh-160022

Website: www.engineerscareergroup.in Toll Free: 1800-270-4242

**E-Mail:** ecgpublica ons@gmail.com | info@engineerscareergroup.in

**GATE-2019:** Analog Circuits | Detailed theory with GATE & ESE previous year papers and detailed solu ons.

©Copyright @2016 by ECG Publica ons (A unit of ENGINEERS CAREER GROUP)

All rights are reserved to reproduce the copy of this book in the form storage, introduced into a retrieval system, electronic, mechanical, photocopying, recording, screenshot or any other form without any prior wri en permission from ECG Publica ons (A Unit of ENGINEERS CAREER GROUP).

First Edi on: 2016

Price of Book: INR 630/-

**ECG PUBLICATIONS** (A Unit of ENGINEERS CAREER GROUP) collected and proving data like: theory for di erent topics or previous year solu ons very carefully while publishing this book. If in any case inaccuracy or prin ng error may nd or occurred then **ECG PUBLICATIONS** (A Unit of ENGINEERS CAREER GROUP) owes no responsibility. The sugges ons for inaccuracies or prin ng error will always be welcome by us.

# CONTENTS

|    | CHAPTER                             | PAGE    |

|----|-------------------------------------|---------|

| 1. | DIODE CIRCUITS                      | 1-81    |

| 2. | BJT BIASING & SMALL SIGNAL ANALYSIS | 82-192  |

| 3. | FREQUENCY RESPONSE                  | 193-216 |

| 4. | OPERATIONAL AMPLIFER & APPLICATION  | 217-314 |

| 5. | FEEDBACK AMPLIFER & OSCILLATOR      | 315-352 |

| 6. | POWER AMPLIFER                      | 353-376 |

| 7. | DIFFERENTIAL AMPLIFIER              | 377-389 |

| 8. | FET & MOSFET                        | 390-434 |

ANALOG CIRCUITS GATE-2019

## CHAPTER - 1 DIODE CIRCUITS

### 1.1 INTRODUCTION

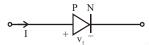

The simplest and most fundamental non-linear circuit element is a diode. Just like a resistor, the diode has two terminals but the diode has a non-linear i-v characteristics.

### 1.1.1 Diode Circuits

DC analysis and models. The ideal diode may be considered the most fundamental non-linear circuit element.

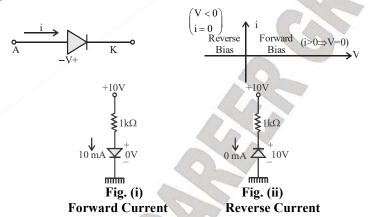

In above fig(i) the diode is conducting. Thus its voltage drop will be zero and the current through it will be determined by the +10V supply and the 1 k $\Omega$  resistor as 10 mA. In fig(ii) the diode is cut off and thus its current will be zero.

### 1.1.2 A Simple Applications

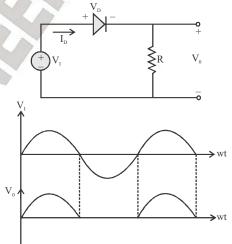

### 1.1.2.1 The Rectifier

The circuit consists of the series connection of a diode D and a resistor R.

# - GATE QUESTIONS

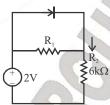

1. An AC voltage source V=10 sin (t) volts is applied to the following network. Assume that  $R_1=3k\Omega,\ R_2=6k\Omega$  and  $R_3=9k\Omega$  and that the diode is ideal.

Rms circuit I<sub>rms</sub> (in mA) through the diode is

[GATE - 2017]

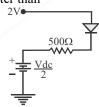

2. The silicon diode, shown in the figure, has a barrier potential of  $0.7~\rm{V}$ . There will be no forward current flow through the diode, if  $V_{dc}$ , in volt, is greater than

[GATE - 2017]

(a) 0.7

(b) 1.3

- (c) 1.8

- (d) 2.6

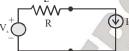

- 3. In the circuit shown below,  $V_s$  is a constant voltage source and  $I_L$  is a constant current load

The value of  $I_L$  that maximizes the power absorbed by the constant current load is

[GATE - 2016]

- (a)  $\frac{V_s}{4R}$

- (b)  $\frac{V_s}{2R}$

- (c)  $\frac{V_s}{R}$

- (d) ∞

- **4.** Assume that the diode in the figure has  $V_{on} = 0.7 \text{ V}$ , but is otherwise ideal.

The magnitude of the current  $i_2$  (in mA) is equal

[GATE - 2016]

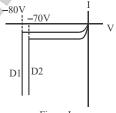

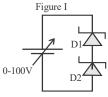

**5.** The I-V characteristics of the zener diodes D1 and D2 are shown in figure 1. These diodes are used in the circuit given in figure II. If the supply voltage is varied from 0 to 100V, then breakdown occurs in

Figure II

[GATE - 2016]

- (a) D1 only

- (b) D2 only

- (c) both D1 and D2

- (d) none of D1 and D2

- **6.** In the circuit shown, assume that the diodes  $D_1$  and  $D_2$  are ideal. The average value of voltage  $V_{ab}$  (in Volts), across terminals 'a' and 'b' is

connected across the load

### [EE ESE - 2015]

- (a) Provides good regulation for all values of load

- (b) Ensure lower PIV of the diodes

- (c) Ensures lower values of capacitance in the

- (d) Reduces ripple content

- 2. A schottky diode is

[EE ESE - 2015]

- (a) A majority carrier device

- (b) A minority carrier device

- (c) A fast recovery diode

- (d) Both majority and minority carrier diode

- 3. Ripple rejection ratio of voltage regulator is the ratio of

### [EE ESE - 2015]

- (a) Output voltage to input ripple voltage

- (b) Output power to input power of regulator

- (c) Input power to output power of regulator

- (d) Input ripple voltage to output ripple voltage

- 4. Which of the following is called 'hot carrier diode?

IEE ESE - 2015

(a) PIN diode

(b) LED

(c) Photo diode

- (d) Schottky diode

- **5.** Compared to an ordinary semiconductor diode a Schottky diode has

### **IEE ESE - 2015**

- (a) Higher reverse saturation current and zero cut-in voltage

- (b) Higher reverse saturation current and higher cut-in voltage

- (c) Higher reverse saturation current and lower cut in voltage

- (d) Lower reverse saturation current and lower cut-in voltage

1. In an L-section filter, a bleeder resistance 6. A silicon diode is preferred to a germanium diode because o fits

[EE ESE - 2015]

- (a) Higher reverse current

- (b) Lower reverse current and higher reverse break down voltage

- (c) Higher reverse current and lower reverse break down voltage

- (d) None of the above

- 7. In a P-N junction diode under reverse bias, the magnitude of electric field is maximum at

### [EE ESE - 2015]

- (a) The edge of the depletion region in the P

- (b) The edge of the depletion region on the N

- (c) The centre of the depletion region on the N side

- (d) The P-N junction

- **8.** A full wave rectifier uses 2 diodes. The internal resistance of each diode is  $20\Omega$ . The transformers RMS secondary voltage from centre tap to each end of secondary is 50V and the load resistance is  $980\Omega$ . Mean load current will be

[EC ESE - 2015]

(a) 45A

(b) 4.5A

(c) 45 mA

(d)  $45\mu A$

**9.** The increase in value of  $\beta$  of transistor can cause the fixed bias circuit to

### [EE ESE - 2014]

- (a) Shift from saturation region to active region

- (b) Shift the operation from active mode to saturation mode

- (c) Shift the operation from saturation mode to cut off mode

- (d) Shift the operation from cut-off mode to active mode

- 10. As compared to an LED, an LCD has the distinct advantage of

ANALOG CIRCUITS GATE-2019

### CHAPTER - 2

### BJT BIASING AND SMALL SIGNAL ANALYSIS

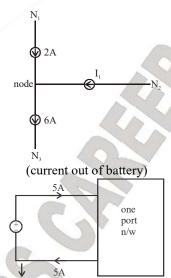

### 2.1 BASIC OF NETWORK

- 1. KCL

- 2. KVL

- 3. Nodal Analysis

### Example.

$I_1 + 2 = 6$

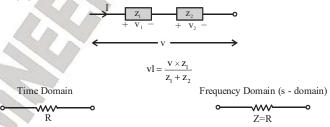

1. Voltage Divider Rule

(current in battery)

$$Z_{c}(s)=Ls=j\omega L$$

$$Z_{c}(s)=\frac{1}{S_{c}}=\frac{1}{j\omega C}$$

# - GATE QUESTIONS

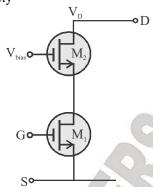

1. Two identical nMOS transistors  $M_1$  and  $M_2$  are connected as shown below. The circuit is used as an amplifier with the input connected between G and S terminals and the output taken between D and S terminals,  $V_{\text{bias}}$  and  $V_D$  are so adjusted that both transistors

are in saturation. The transconductance of this combination is defined as  $g_m = \frac{\partial i_D}{\partial v_{GS}}$  while

the output resistance is  $r_{_{0}}=\frac{\partial v_{_{DS}}}{\partial i_{_{D}}}\,,$  where  $i_{D}$  is

the current flowing into the drain of  $M_2$ . Let  $g_{m1}$ ,  $g_{m2}$  be the transcondcutances and  $r_{o1}$ ,  $r_{o2}$  be the output resistance of transistors  $M_1$  and  $M_2$ , respectively

Which of the following statements about estimates for  $g_m$  and  $r_0$  is correct?

[GATE - 2018]

- (a)  $g_m \approx g_{m1}$  .  $g_{m2}$  .  $r_{02}$  and  $r_0 \approx r_{01} + r_{02}$

- (b)  $g_m \approx g_{m1} + g_{m2}$  and  $r_0 \approx r_{01} + r_{02}$

- (c)  $g_m \approx g_{m1}$  and  $r_0 \approx r_{01}$  .  $g_{m2}$  .  $r_{02}$

- (d)  $g_m \approx g_{m1}$  and  $r_0 \approx r_{02}$

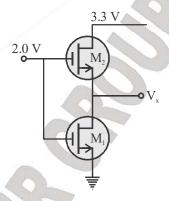

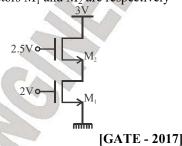

- 2. In the circuit shown below, the (W/L) value for  $M_2$  is twice that for  $M_1$ . The two nMOS transistors are otherwise identical. The threshold voltage  $V_T$  for both transistors is 1.0 V. Note that  $V_{GS}$  for  $M_2$  must be > 1.0 V

Current through the nMOS transistors can be modeled as

$$I_{DS} = \mu C_{ox} \left(\frac{W}{L}\right) \left(\left(V_{GS} - V_{T}\right)V_{DS} - \frac{1}{2}V_{DS}^{2}\right) for \ V_{DS} \leq V_{GS} - V_{T}$$

$$I_{DS} = \mu C_{ox} \left(\frac{W}{L}\right) (V_{GS} - V_{T}) / 2 \text{ for } V_{DS} \le V_{GS} - V_{T}$$

The voltage (in volts, accurate to two decimal places) at  $V_x$  is \_\_\_\_\_\_.

[GATE - 2018]

**3.** An npn biplar junction transistor (BJT) is operating in the active region. If the reverse bias across the base-collector junction is increased, then

[GATE - 2017]

- (a) The effective base width increase and common-emitter current gain increases

- (b) The effective base width increase and common-emitter current gain decreases

- (c) The effective base width decrease and common-emitter current gain increases

- (d) The effective base width decrease and common-emitter current gain decreases

- **4.** Consider the circuit shown in figure. Assume base to emitter voltage  $V_{BE} = 0.8V$  and common base current gain ( $\alpha$ ) of transistor is unity

**1.** A transistor is connected in CE configuration (a) 1, 2 and 4 only with  $V_{CC} = 10V$ . The voltage drop across the  $600\Omega$  resistor in the collector circuit is 0.6V. If  $\alpha = 0.98$ , the base current is nearly

[EC ESE - 2018]

(a) 6.12 mA

(b) 2.08 mA

(c) 0.98 mA

(d) 0.02 mA

2. A single stage amplifier has a voltage gain of 100. The load connected to the collector is  $500\Omega$  and its input impedance is  $1k\Omega$ . Two such stages are connected in cascade through an RC coupling. The overall gain is

[EC ESE - 2016]

(a) 10000

(b) 6666.66

(c) 5000

(d) 1666.66

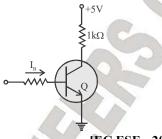

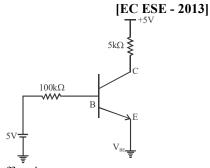

3. Assuming  $V_{CE}$  (Sat) = 0.3V for a silicon transistor at ambient temperature of 25°C and  $h_{FE} = 50$ , the minimum base current  $I_B$  required to drive the transistor into saturation for the circuit shown is

[EC ESE - 2016]

(a) 64µA

(b) 78 µA

(c) 94 µA

(d) 140 uA

- 4. Which of the following regions of operations are mainly responsible for heating of the transistor under switching operation?

- 1. Saturations region

- 2. Cut off region

- 3. Transition from saturation to cut off

- 4. Transition from cut off to saturation select the correct answer using the codes given below:

[EC ESE - 2016]

- (b) 1, 3 and 4 only

- (c) 2 and 3 only

- (d) 1 and 3 only

- 5. Consider the following statements regarding linear power supply.

- 1. It requires low frequency transformer.

- 2. It requires high frequency transformer.

- 3. The transistor works in active region. Which of the above statements is/are correct?

[EC ESE - 2016]

(a) 1 only

(b) 2 and 3 only

(c) 1 and 3 only

(d) 3 only

**6.** The most commonly used configuration for use as a switching device is

[EC ESE - 2016]

- (a) Common base configuration

- (b) Common collector configuration

- (c) Collector emitter shorted configuration

- (d) Common emitter configuration

- 7. The value of  $h_{FE}$  (the hybrid parameters) of a Common - Emitter (CE) connection of a bipolar Junction Transistor (BJT) is given as 250. What is the value of  $\alpha_{dc}$  (ratio of collector current to emitter current), for this BJT?

[EC ESE - 2016]

(a) 0.436

(b) 0.656

(c) 0.874

(d) 0.996

8. The h-parameters of a CE amplifier feeding a load of  $10k\Omega$  are  $h_{ie} = 1k\Omega$ ,  $h_{fe} = 50$ ,  $h_{re} = 0$ , and  $1/h_{oe} = 40 \text{ k}\Omega$ . The voltage gain would be

[EC ESE - 2015]

(a) -40

(b) -100

(c) -400

(d) -500

- 9. Consider the following statements pertaining to frequency response of RC coupled amplifier.

- 1. Coupling capacitance affects high frequency response

- 2. Bypass capacitance affects high frequency response

### CHAPTER - 3

### FREQUENCY RESPONSE

### 3.1 CAPACITORS

There are three types of capacitors

- 1. Coupling Capacitor

- 2. Emitter Capacitor

- 3. Junction Capacitance/ Internal Capacitance

To determine the gain of amplifier with respect to itself frequency we need to do frequency analysis of amplifier in which response of the amplifier is studied over the range of frequency.

Slope of DC Load Line =

$$-\frac{1}{R_C}$$

Slope of AC Load Line,

$$m = -\frac{1}{R_L} = -\left(\frac{1}{R_C} + \frac{1}{R_L}\right)$$

$$\therefore R_{L} = \frac{1}{\left(\frac{1}{R_{C}} + \frac{1}{R_{L}}\right)}$$

The slope of AC line is greater as compared to slope of DC line.

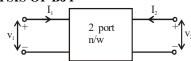

### 3.2 H-PARAMETER ANALYSIS OF BJT

$$\begin{split} &V_1 = f\left(I,\,V_2\right) \\ &I_2 = f\left(I,\,V_2\right) \\ &V_1 = h_{11}\,I_1 + h_{12}\,V_2 \\ &I_2 = h_{21}\,\,I_1 + h_{22}\,V_2 \end{split}$$

# **GATE QUESTIONS**

superheterodyne receiver, intermediate frequency is 15 MHz and the local oscillator frequency is 3.5 GHz. If the frequency of the received signal is greater than the local oscillator frequency, then the image frequency (in MHz) is

[GATE - 2016]

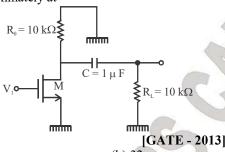

2. The ac schematic of an NMOS commonsource stage is shown in the figure below, where part of the biasing circuits has been omitted for simplicity. For the n-channel MOSFET M, the transconductance gm = 1 mA/V, and body effect are to be neglected. The lower cut-off frequency in Hz of the circuit is approximately at

(a) 8 (c) 50 (b) 32(d) 200

3. A bipolar transistor is operating in the active region with a collector current of 1 mA. Assuming that the  $\beta$  of the transistor is 100 and the thermal voltage  $(V_T)$  is 25 mV, the transconductance (gm) and the input resistance  $(r\pi)$  of the transistor in the common emitter configuration, are

[GATE - 2004]

(a)

$$g_m = 25 \text{mA/V}$$

and  $r_\pi = 15.625 \text{ k}\Omega$

(b)

$$g_m = 40 \text{mA/V}$$

and  $r_\pi = 4.0 \text{ k}\Omega$

(c)

$$g_m = 25 \text{mA/V}$$

and  $r_\pi = 2.5 \text{ k}\Omega$

(d)

$$g_m = 40 \text{mA/V}$$

and  $r_\pi = 2.25 \text{ k}\Omega$

4. Three identical amplifiers with each one having a voltage gain of 50, input resistance of 1 k $\Omega$  and output resistance of 250  $\Omega$ , are cascaded. The open circuit voltage gain of the combined amplifier is

[GATE - 2004]

(a) 49 dB

(b) 51 dB

(c) 98 dB

(d) 102 Db

5. An npn BJT has  $g_m=38$  mA/V,  $C_\mu=10^{-14}F$ ,  $C_\pi=4\times10^{-13}$  F, and DC current gain  $\beta_0=90$ . For this transistor  $f_T$  and  $f_B$  are

**IGATE - 20011**

(a)  $f_T = 1.64 \times 10^8$  Hz and  $f_\beta = 1.47 \times 10^{10}$  Hz (b)  $f_T = 1.47 \times 10^{10}$  Hz and  $f_\beta = 1.47 \times 10^{10}$  Hz (c)  $f_T = 1.33 \times 10^{12}$  Hz and  $f_\beta = 1.47 \times 10^{10}$  Hz (d)  $f_T = 1.47 \times 10^{10}$  Hz and  $f_\beta = 1.33 \times 10^{12}$  Hz

6. An amplifier is assumed to have a single-pole high-frequency transfer function. The rise time of its output response to a step function input is 35 nsec. The upper-3 dB frequency (in MHz) for the amplifier to a sinusoidal input is approximately at

[GATE - 1999]

(a) 4.55

(b) 10

(c) 20

(d) 28.6

7. An npn transistor (with C = 0.3 pF0 has unity - gain cutoff frequency fT of 400 \*\*\* at a dc bias current Ic = 1 mA. The value of its  $C\mu$  (in pF) is approximately (VT = 26 m\*\*) is

[GATE - 1999]

(a) 15 pF

(b) 12 pF

(c) 17 pF

(d) 10 pF

**8.** The fT of a BJT is related to its gm,  $C\pi$  and Cu as follows

[GATE - 1996]

(a)

$$f_T = \frac{C_{\pi} + C_{\mu}}{g_{m}}$$

(a)

$$f_T = \frac{C_{\pi} + C_{\mu}}{g_m}$$

(b)  $f_T = \frac{2\pi(C_{\pi} + C_{\mu})}{g_m}$

frequencies. This is due to

**IEC ESE-20181**

- (a) Coupling and bypass capacitors

- (b) Early effect

- (c) Inter electrode transistor capacitances

- (d) The fact that reactance becomes high

- 2. The n-p-n transistor made of silicon has a DC base bias voltage 15 V and an input base resistor 150 K $\Omega$ . Then the value of the base current into the transistor is

[EC ESE-2017]

- (a)  $0.953 \mu A$

- (b) 9.53µA

- (c) 95.3µA

- (d) 953µA

- 3. The capacitance of a full wave rectifier, with 60hz input signal, peak output voltage  $V_p = 10v$ , load resistance  $R = 10k\Omega$  and input ripple voltage  $V_r = 0.2V$ , is

**IEC ESE - 2016**

- (a)  $22.7 \mu F$

- (b)  $33.3 \mu F$

- (c)  $41.7 \mu F$

- (d)  $83.4 \mu F$

- **4.** A full wave rectifier connected to the output terminals of the mains transformer produces and RMS voltage of 18V across the secondary. The no - load voltage across the secondary of the transformer is

[EC ESE - 2016]

- (a) 1.62 V

- (b) 16.2 V

- (c) 61.2 V

- (d) 6.12 V

- 5. A power supply uses bridge rectifier with capacitor input filter. If one of the diodes is defective, then

- 1. The dc load voltage will be lower than it expected value.

- 2. Ripple frequency will be lower than its expected value.

- 3. The surge current will increase manifold Which of the above statements are correct?

**IEC ESE - 2015**

- (a) 1 and 2 only

- (b) 1 and 3 only

- (c) 2 and 3 only

- (d) 1, 2 and 3

1. The gain of a bipolar transistor drops at high 6. In an L-section filter, a bleeder resistance is connected across the load to

[EC ESE - 2015]

- (a) Provide good regulation for all values of

- (b) Ensure lower PIV of the diodes

- (c) Ensure lower values of capacitance in the filter

- (d) Reduce ripple content

- 7. In a voltage regulator, zener diode is

- 1. connected in series with filter output

- 2. Forward biased

- 3. Connected in parallel with filter output

- 4. Reversed biased

Which of the above are correct

[EC ESE - 2015]

- (a) 1 and 2

- (b) 3 and 4

- (c) 1 and 4

- (d) 2 and 3

- 8. With the increase of reverse bias in a p-n diode, the reverse current

[EC ESE - 2013]

- (a) Decreases

- (b) Increases

- (c) Remains constant

- (d) May increase or decrease depending upon doping

- 9. The transistor as shown in the circuit is operating in:

- (a) Cut off region

- (b) Saturation region

- (c) Active region

- (d) Either in active or saturation region

ANALOG CIRCUITS GATE-2019

### **CHAPTER - 4**

### OPERATIONAL AMPILIFIER AND APPLICATIONS

### 4.1 INTRODUCTION

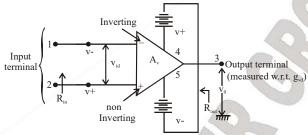

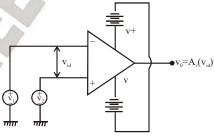

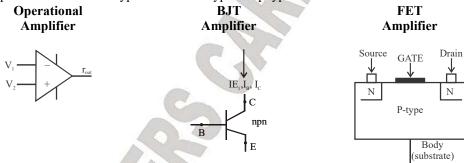

Operational amplifier is a d.c. coupled high gain voltage amplifier.

Operational amplifier is available in IC form and it can be obtained in 7 pin ICs or more than 14 pin IC's and many more.

v<sup>+</sup> and v<sup>-</sup> are d.c. supplies

v<sup>+</sup> and v<sup>-</sup> are the two dc power supplies which are necessary for its working.

$\mathbf{v}_{id} = \mathbf{v}_{+} - \mathbf{v}_{-}$

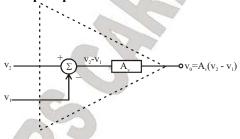

### 4.1.1 Mathematical Model of Op-amp

Op-amp is design to sense the difference between voltage signal to applied between its two input signal.

$v_1$  and  $v_2$  are the voltage applied w.r.t ground.

If

$$v_1 = v_2 = v : v_0 = Av [v - v] = 0$$

.

If we provide same input at both end then the output will be zero ideally.

Hence in ideal op-amp common voltage should be zero.

# **GATE QUESTIONS**

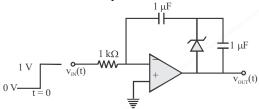

1. In the circuit shown below, the op-amp is ideal and Zener voltage of the diode is 2.5 volts. At the input, unit step voltage is applied i.e. $v_{IN}(t) = u(t)$  volts. Also at t = 0, the voltage across each of the capacitors is zero

The time t, in milliseconds, at which the output voltage v<sub>OUT</sub> crosses -10 V is

[GATE - 2018]

- (a) 2.5

- (b) 5

- (c) 7.5

- (d) 10

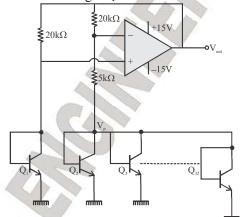

2. In the voltage reference circuit shown in the figure, the op-amp is ideal and transistors  $Q_1$ ,  $Q_2$ ....., Q<sub>32</sub> are identical in all respects and have infinitely large values of common-emitter current gain (β). The collector current (I<sub>c</sub>) of the transistors is related to their base emitter voltage  $(V_{BE})$  by the relation  $I_C = I_S \exp (V_{BE}/V_T)$ ; where I<sub>s</sub> is the saturation current. Assume that the voltage V<sub>p</sub> shown in the figure is 0.7V nad the thermal voltage  $V_T = 26 \text{mV}$

The output voltage Vout (in volts) is

[GATE - 2017]

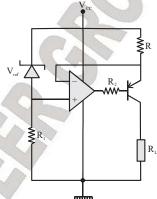

3. Consider the constant current source shown in the figure below. Let  $\beta$  represent the current gain of the transistor

The load current I<sub>0</sub> through RL is

[GATE - 2017]

(a)

$$I_0 = \left(\frac{\beta+1}{\beta}\right) \frac{V_{\text{ref}}}{R}$$

(b)  $I_0 = \left(\frac{\beta}{\beta+1}\right) \frac{V_{\text{ref}}}{R}$

(b)

$$I_0 = \left(\frac{\beta}{\beta + 1}\right) \frac{V_{ref}}{R}$$

(c)

$$I_0 = \left(\frac{\beta+1}{\beta}\right) \frac{V_{ref}}{2R}$$

$$\left(\frac{\beta+1}{\beta}\right)\frac{V_{\text{ref}}}{2R}$$

(d)  $I_0 = \left(\frac{\beta}{\beta+1}\right)\frac{V_{\text{ref}}}{2R}$

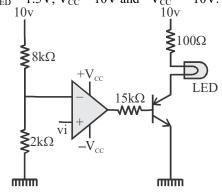

4. The following signal V<sub>i</sub> of peak voltage 8V is applied to the non-inverting terminal of an ideal Opamp. The transistor has  $V_{BE} = 0.7V$ ,  $\beta = 100$ ;  $V_{LED} = 1.5V$ ,  $V_{CC} = 10V$  and  $-V_{CC} = -10V$ .

1. If the input (V<sub>in</sub>) to the circuit is a sine wave, | 5. In an Op-Amp, if the feedback voltage is the output will be

**IEE ESE - 2017**

- (a) Half-wave rectified sine wave

- (b) Full-wave rectified sine wave

- (c) Triangular wave

- (d) Square wave

- 2. If an input impedance of op-amp is finite, then which one of the following statements related to virtual ground is correct?

[EE ESE - 2017]

- (a) Virtual ground condition may exist

- (b) Virtual ground condition cannot exist

- (c) In case of op-amp, virtual ground condition always exists

- (d) Cannot make a valid declaration

- 3. Hysteresis is desirable in a Schmidt-trigger because

[EE ESE - 2017]

- (a) Energy is to be stored/discharged in parasitic capacitances

- (b) Effects of temperature variations would be compensated

- (c) Devices in the circuit should be allowed time for saturating and dee-saturation

- (d) It would prevent noise from causing false triggering

- 4. An Op-Amp can be connected to provide

- 1. Voltage controlled current source

- 2. Current controlled voltage source

- 3. Current controlled current source which of the above statements are correct?

[EE ESE - 2016]

- (a) 1 and 2 only

- (b) 1 and 3 only

- (c) 2 and 3 only

- (d) 1, 2 and 3

- reduced by connecting a voltage divider at the output. Which of the following will happen?

- 1. Input impedance increases

- 2. Output impedance reduces

- 3. Overall gain increases

Which of the above statements is/are correct?

[EE ESE - 2016]

- (a) 1 only

- (b) 2 only

- (c) 3 only

- (d) 1, 2 and 3

**6.** The transient response rise time (unity gain) of an Op-Amp is 0.05 µs. The small signal bandwidth is

[EE ESE - 2016]

- (a) 7 kHz

- (b) 20 kHz

- (c) 7 MHz

- (d) 20MHz

- 7. A negative feedback of  $\beta = 2.5 \times 10^{-3}$  is applied to an amplifier of open - loop gain 1000. What is the change in overall gain of the feedback amplifier, if the gain of the internal amplifier is reduced by 20%?

[EE ESE - 2016]

- (a) 295.7

- (b) 286.7

- (c) 275.7

- (d) 266.7

8. Statement (I): An ideal op- amp should have infinite bandwidth

Statement II: An ideal op amp should have infinite input resistance and zero output resistance

[EE ESE - 2015]

### **Codes:**

- (a) Both Statement (I) and Statement (II) are individually true and Statement (II) is the correct explanation of Statement (I)

- (b) Both statement (I) and Statement (II) are individually true but statement (II) is not the correct explanation of statement (I)

- (c) Statement (I) is true but statement (II) is false

- (d) Statement(I) is false but statement (II) is true

ANALOG CIRCUITS GATE-2019

### **CHAPTER - 5**

### FEEDBACK AMPLIFIER AND OSCILLATOR

### 5.1 FEEDBACK ARE OF TWO TYPES

- 1. Regenerative feedback [+ve (oscillators) feedback]

- 2. Degenerative feedback [-ve (amplifier) feedback]

In amplifier design negative feedback is applied to effect one or more of the following property Feedback in practical case is never 100%.

Feedback decide the fraction of output which is given back to the input.

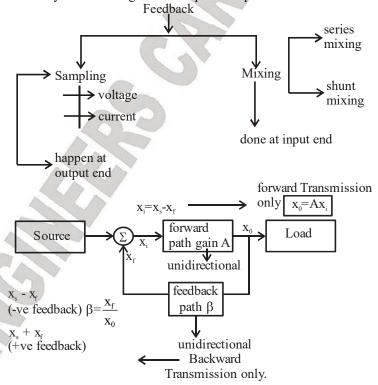

### 5.1.1 General structure of the feedback

- 1. Gain =  $\frac{\text{output}}{\text{input}}$   $\Rightarrow$  finite [for all practical stable system]

- 2. Gain = finite  $\rightarrow$  mean output following input

- 3. Gain  $\Rightarrow \infty \Rightarrow \frac{\text{finite}}{\text{zero}} \rightarrow \frac{\text{output}}{\text{input}} \Rightarrow \text{unstable system}$

If gain is finite then output is finite for zero input. If this arrangement is intended arrangement then the system arrangement is stable. If the gain f the system become finite by chance then the system is unstable became the system with  $\infty$  gain are not practical possible.

# - GATE QUESTIONS

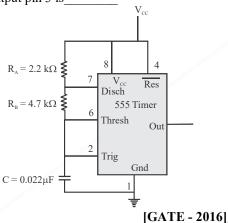

1. In the table multivibrator circuit shown in the figure, the frequency of oscillation (in kHz) at the output pin 3 is

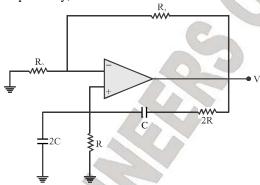

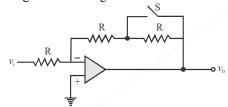

2. The circuit shown in the figure has an ideal

opamp. The oscillation frequency and the condition to sustain the oscillations, respectively, are

[GATE - 2015]

(a)

$$\frac{1}{CR}$$

and  $R_1 = R_2$

(b)

$$\frac{1}{CR}$$

and  $R_1 = 4R_2$

(c)

$$\frac{1}{2CR}$$

and  $R_1 = R_2$

(d)

$$\frac{1}{2CR}$$

and  $R_1 = 4R_2$

**3.** The desirable characteristics of a transconductance amplifier are

[GATE - 2014]

(a) High input resistance and high output resistance

(b)High input resistance and low output resistance

(c)Low input resistance and high output resistance

(d)Low input resistance and low output resistance

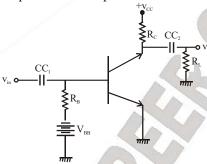

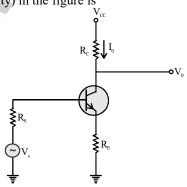

**4.** The feedback topology in the amplifier circuit (the base bias circuit is not shown for simplicity) in the figure is

[GATE - 2014]

- (a) Voltage shunt feedback

- (b) Current series feedback

- (c) Current shunt feedback

- (d) Voltage series feedback

- **5.** In the ac equivalent circuit shown in the figure, if  $i_{in}$  is the input current and  $R_F$  is very large, the type of feedback is

1. An amplifier, without feedback, has a gain A. 1. The tank circuit of a Hartley oscillator is distortion is reduced to 2% with negative inductor. feedback (feedback factor  $\beta = 0.03$ ). The values of A and A'(i.e, the gain with feedback) are, respectively, nearly

[EC ESE - 2018]

(a) 133.3 and 18.5

(b) 133.3 and 26.7

(c) 201.3 and 26.7

(d) 201.3 and 18.5

2. In a sinusoidal oscillator, sustained oscillator will be produced only if the loop gain (at the oscillation frequency) is

[EC ESE - 2016]

- (a) Less than unity but not zero

- (b) Zero

- (c) Unity

- (d) Greater than unity

- 3. Consider the following statements regarding Wien Bridge oscillator:

- 1. It has a larger banwidth than the phase shift oscillator

- 2. It has a smaller bandwidth than the phase shift oscillator

- 3. It has 2 capacitor while the phase shift oscillator has 3 capacitors.

- 4. It has 3 capacitors while the phase shift oscillator has 2 capacitors.

Which of the above statements are correct?

[EC ESE - 2016]

(a) 1 and 3 only

(b) 2 and 4 only

(c) 1 and 4 only

(d) 2 and 3 only

**4.** If the quality factor of a single-tuned amplifier is doubled, the bandwidth will

[EC ESE - 2016]

- (a) Remain the same

- (b) Become ball

- (c) Become double

- (d) Become four times

- 5. Consider the following statements related to oscillator circuits.

- The distortion at full output is 10%. The made up of a tapped capacitor and a common

- 2. The than circuit of a Colpitts oscillator is made up of a tapped capacitor and a common oscillator.

- 3. The wien bridge oscillator is essentially a two -stage amplifier with an RC bridge in the first stage and the second stage serving as an inverter.

- 4. Crystal oscillators are fixed frequency oscillators with a high Q - factor.

Which of the above statements are correct?

[EC ESE - 2016]

(a) 1, 2 and 3 only

(b)  $\overline{2}$ , 3 and 4 only

(c) 1, 2 and 4 only

- (d) 1, 3 and 4 only

- **6.** A negative feedback of  $\beta = 2.5 \times 10^{-3}$  is applied to an amplifier of open-loop gain 1000. What is the change in overall gain of the feedback amplifier, if the gain of the internal amplifier is reduced by 20%?

[EE ESE - 2016]

(a) 295.7

(b) 286.7

(c) 275.7

(d) 266.7

7. In order to generate a square wave form a sinusoidal input signal, one can use

[EE ESE - 2015]

- 1. Schmitt trigger circuit

- 2. Clippers and amplifiers

- 3. Monostable multivibrator

Which of the above statements are correct?

- (a) 1, 2 and 3

- (b) 1 and 2 only

- (c) 1 and 3 only

- (d) 2 and 3 only

- 8. In a voltage-series feedback amplifier with open loop gain  $A_v$  and the feedback factor  $\beta$ , the input resistance becomes

[EE ESE - 2015]

### CHAPTER - 6

### **POWER AMPLIFIERS**

### 6.1 POWER AMPLIFIER/LARGE SIGNAL AMLIFIER

- 1. It is the last stage in multistage amplifier.

- 2. It is defined as ability of amplifier to convert available output dc power into ac power with the application of input signal.

### **6.2 HARMONIC DISTORTION**

- 1. In a power amplifier, signal amplitudes is very large. Hence signal is operated in linear & non-linear portion of input characteristics. So we get harmonics in output and harmonic distortion is present at output.

- 2. It is a non-linear distortion.

- 3. Fourier series expansion of collator current of power transistor is:

$$i_c = I_c + B_0 + B_1 \cos \omega t + B_2 \cos 2\omega t + \dots$$

where  $I_c + B_0$  is DC

B<sub>1</sub>cosωt is fundamental

B<sub>2</sub>cos2ωt is harmonics

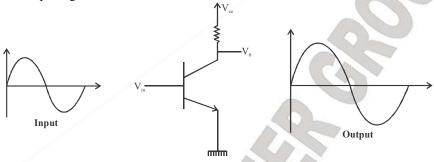

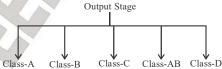

### 6.3 CLASSIFICATION OF OUTPUT STAGE

Output stages are classified according to the collector current wave form that result when an input is applied

Second harmonic distortion,  $D_2 = \frac{B_2}{B_1}$

Third harmonic distortion,  $D_3 = \frac{B_3}{B_1}$

AC power output due to fundamental component

$$P_{ac} = I_{rms}^2 R_0 = \left(\frac{B_1^2}{2}\right) R_0 \Rightarrow P_0$$

# — GATE QUESTIONS

**1.** Which one of the following statements is correct about an ac-coupled common-emitter amplifier operating in the mid band region?

[GATE - 2016]

- (a) The device parasitic capacitances behave like open circuits, whereas coupling and bypass capacitances behave like short circuits.

- (b) The device parasitic capacitances coupling capacitances and bypass capacitances behave like open circuits.

- (c) The device parasitic capacitances, coupling capacitances and bypass capacitances behave like short circuits.

- (d) The device parasitic capacitances behave like short circuits, whereas coupling and bypass capacitances behave like open circuits.

- **2.** Crossover distortion behavior is characteristic of

[GATE - 1999]

- (a) Class A output stage

- (b) Class B output stage

- (c) Class AB output stage

- (d) Common-base output stage

- 3. A power Amplifier delivers 50 W output at 50% efficiency. The ambient temperature is 25°C. If the maximum allowable junction temperature is 150°C, then the maximum thermal resistance  $\theta g_c$  that can be tolerated is

**IGATE - 1995**]

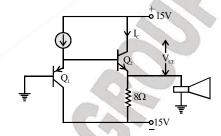

4. The circuit shown in the figure supplies power to on  $8\Omega$  speaker, LS. The values of  $I_C$  and  $V_{CE}$  for this circuit will be  $I_C =$  \_\_\_\_ and  $V_{CE}$

[GATE - 1995]

**5.** A class-A transformer coupled, transistor power Amplifier is required to deliver a power output of 10 watts. The maximum power Rating of the transistor should not be less than

[GATE - 1994]

- (a) 5W

- (b) 10W

- (c) 20W

- (d) 40W

6. In a transistor push-pull Amplifier

[GATE - 1993]

- (a) There is no d.c. present in the output

- (b) There is no distortion in the output

- (c) There is no even harmonics in the output

- (d) There is no add harmonics in the output

- 7. In case of class A amplifiers the ratio (efficiency of transformer coupled amplifier)/(efficiency of a transformer less amplifier) is

[GATE - 1987]

(a) 2.9

(b) 1.36

- (c) 1.0

- (d) 0.5

# - SEE OBJ QUESTIONS

1. The Class-B- pull amplifier is an efficient two-transistor circuit, in which the two transistors operate in the following way:

5. A power amplifier with a gain of 100∠0° has an output of 12v at 1.5 kHz along with a second harmonic content of 25 percent. A negative

[EE ESE - 2016]

- (a) Both transistors operate in the active region throughout the negative ac cycle

- (b) Both transistors operate in the active region for more than half cycle but less than a whole cycle

- (c) One transistor conducts during the positive half-cycle and the other during the negative half-cycle

- (d) Full supply voltage appears across each of the transistors

- 2. Which of the following is the principal factor that contributes to the doubling of the conversion efficiency in a transformer coupled amplifier?

[EE ESE - 2015]

- (a) Reducing the power dissipated in the transistor

- (b) Eliminating the power dissipation in the transformer

- (c) Elimination of dc power dissipated in the load

- (d) Impedance matching of the transformer

- **3.** A power amplifier operated from 12v battery gives an output of 2W. The maximum collector current in the circuit is

**IEC ESE - 2015**

- (a)  $166.7 \, \mu A$

- (b) 166.7mA

- (c) 166.7 mA

- (d) 16.67 mA

- **4.** For a transformer, the load connected to the secondary has an impedance of  $8\Omega$ . Its reflected impedance on primary is observed to be  $648\Omega$ . The turns ratio of this transformer is

[EE ESE - 2014]

- (a) 6:1

- (b) 10:1

- (c) 9:1

- (d) 8:1

**5.** A power amplifier with a gain of  $100\angle0^\circ$  has an output of 12v at 1.5 kHz along with a second harmonic content of 25 percent. A negative feedback is to be provided to reduce the harmonic content of the output to 2.5 percent. What should be the gain of the feedback path and the level of signal input to the overall system, respectively?

[EE ESE - 2014]

- (a) 0.9 and 0.12 V

- (b) 0.9 and 12 V

- (c) 0.09 and 1.2 V

- (d) 9 and 0.12V

- **6.** An output signal of a power amplifier has amplitudes of 2.5 V fundamental, 0.25 V, second harmonic and 0.1 V third harmonic. The total percentage harmonic distortion of the signal is

[EC ESE - 2012]

- (a) 12.8%

- (b) 10.8%

- (c) 6.4%

- (d) 1.4%

- 7. The second-harmonic component in the output of a transistor amplifier, without feedback, is  $B_2$ . The second harmonic component, with negative feedback  $B_2$ ' is equal to (where A = Amplifier gain and  $\beta =$  feedback factor).

[EC ESE - 2012]

- (a)  $\frac{B_2}{1 + \Delta B}$

- (b)  $B_2 (1 + A\beta)$

- (c)  $\frac{B_2}{\beta}$

- (d)  $\frac{B_2}{AB}$

- **8. Statement (I)**: Much of the distortion introduced in large signal amplifiers is eliminated by push –pull circuit

**Statement (II)**: The signals applied to the two transistors applied to the two transistors in push-pull mode are 180° out of phase

[EE ESE - 2012]

### **CHAPTER - 7**

### DIFFERENTIAL AMPLIFIERS

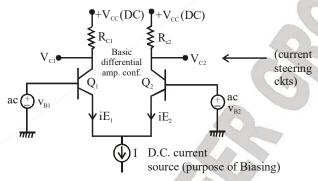

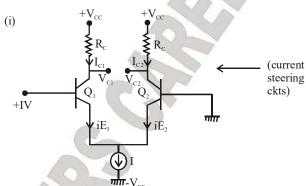

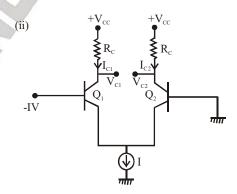

### 7.1 DIFFERENTIAL AMPLIFIER (BJT PAIR)

It is also known as emitter coupled differential amplifier. It consist of 2 matched transistor  $Q_1$  and  $Q_2$ , whose emitters are joined together.

$$\begin{split} \frac{v_{cc} - v_{c1}}{R_c} &= I_{c_1} \\ v_{cc} - I_{c1} R_c &= v_{c1} \\ v_{cc} - I_{c2} R_c &= v_{c2} \end{split}$$

1. The magnitude of the gain  $\frac{V_0}{V_i}$  in the

inverting op-amp circuit shown in the figure is x with switch S open. When switch S is closed, the magnitude of the gain will be

[EE ESE - 2018]

(a) x

(b)  $\frac{x}{2}$

(c) 2x

- (d)  $\frac{2}{x}$

- 2. An op-amp is used in a notch filter. The notch frequency is 2 kHz, lower cut-off frequency is 1.8 kHz and upper cut-off frequency is 2.2 kHz. Then Q of the notch filter is

[EE ESE - 2018]

- (a) 3.5

- (b) 4.0

- (c) 4.5

- (d) 5.0

- 3. In op-amp based inverting amplifier with a gain of 100 and feedback resistance of  $47k\Omega$ , the op amp input offset voltage is 6 mV and input bias current is 500 nA. The output offset voltage due to an input offset voltage and an input bias current, are

[EE ESE - 2018]

- (a) 300 mV and 23.5 mV

- (b) 606 mV and 47.0 mV

- (c) 300 mV and 47.0 mV

- (d) 606 mV and 23.5 mV

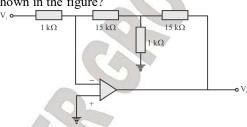

- **4.** What is the gain of the amplifier circuit as shown in the figure?

[EE ESE - 2018]

- (a) 255 (c) -31

- (b) 31 (d) –255

- 5. Statement (I):

In ideal case, the inverting and non-inverting input terminals of an operational amplifier are almost at the same potential.

### Statement (II):

It is common practice to connect the inverting and non – inverting terminals to the same point.

### **Codes:**

[EE ESE - 2018]

- (a) Both Statement (I) and Statement (II) are individually true and Statement (II) is the correct explanation of Statement (I)

- (b) Both Statement (I) and Statement (II) are individually true but Statement (II) is not the correct explanation of Statement (I)

- (c) Statement (I) is true but Statement (II) is false

- (d) Statement (I) is false but Statement (II) is true

### **CHAPTER - 8**

### FET AND MOSFET

### 8.1 INTRODUCTION

$$\omega_{\text{dep}} = \left[\frac{2 \in \left[\frac{1}{\text{q}} \left[\frac{1}{N_{\text{A}}} + \frac{1}{N_{\text{B}}}\right] \left[v_{\text{bi}} + v_{\text{R}}\right]^{Y_{2}}\right]^{1/2}\right]$$

$\omega_{dep}$  = Basic depletion with standard formula  $v_{bi}$  = Built in potential or contact potential

$$v_{bi} = V_T \ln \left[ \frac{N_A N_D}{n_i} \right]$$

$v_R$  = applied reverse biased

### 8.1.1 Field Effect Transistor is an unpolar device

- 1. JFET-n-type and p-type

- 2. MOSFET

- (i) Depletion type MOSFET-n type and p type

- (ii) Depletion Enhancement type MOSFET-n type and p type

- 3. FET is a unipolar device because the current conduct only due to majority carrier this is known as the field effect transistor.

- 4. It is field effect transistor that is in which current is controlled by electric field and there is not leakage current and it is less noisy as compared to BJT.

- 5. Source, Drain and Gate are these Basic terminal of any FET device.

### **8.1.2 Source**

It is the terminal through which majority carriers enter the bar-since carrier come from it ie why is called as source.

### 8.1.3 **Drain**

It is the terminal through which majority carrier leaves the channel. They are drain out from this terminal.

# **GATE QUESTIONS**

1. An n-channel enhancement mode MOSFET (c) Linear, Saturation is biased at VBS > VTH and VDSD > (VBS -VTH), where VGS is the gate to source voltage, VDS is the drain to source voltage and VTH is the threshold voltage. Considering channel length modulation effect to be significant, the MOSFET behaves as a

[GATE - 2017]

- (a) Voltage source with zero output impedence

- (b) Voltage source with non-zero output impedence

- (c) Current source with finite output impedence

- (d) Current infinite output source with impedence

- 2. A MOS capacitor is fabricated on p-type Si (silicon) where the metal work function is 4.1eV and electron affinity of Si is 4.0eV,  $E_C - E_F =$ 0.9eV; where E<sub>C</sub> and E<sub>F</sub> are conduction band minimum and the Fermi energy levels of Si, respectively. Oxide  $\varepsilon_r = 3.9$ ,  $\varepsilon_0 = 8.85 \times 10^{-14}$ F/cm, oxide thickness  $t_{ox} = 0.1 \mu m$  and electron charge  $q = 1.6 \times 10^{-19}$  C. If the measured flat band voltage of this capacitor is -1V, then the magnitude of the fixed charge at the oxide semiconductor interface, in nC/cm+, is

[GATE - 2017]

3. Assuming that transistors  $M_1$  and  $M_2$  are identical and have a threshold voltage of 1V, the state of transistors M<sub>1</sub> and M<sub>2</sub> are respectively

- (a) Saturation, Saturation

- (b) Linear, Linear

- (d) Saturation, Linear

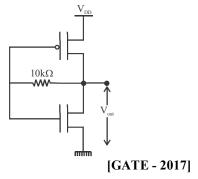

- **4.** In the circuit shown, transistor  $Q_1$  and  $Q_2$  are biased at a collector current of 2.6mA. Assuming the transistor current gains are sufficiently large to assume collector current equal to emitter current and thermal voltage of 26mV, the magnitude of voltage gain V<sub>0</sub>/V<sub>s</sub> in the mid band frequency range is (up to second decimal place).

[GATE - 2017]

- 5. Consider the following statements for a metal oxide semiconductor field after effect transistor (MOSFET)

- P: As channel length reduces, OFF-state current

- Q: As channel length reduces, output resistance increases

- R: As channel length reduces, threshold voltage remains constant

- S: As channel reduces, ON current increases Which of the above statements are **INCORRECT?**

[GATE - 2017]

- (a) P and O

- (b) P and S

- (c) Q and R (d) R and S

- 6. What is the voltage V<sub>out</sub> in the following circuit?

1. When the drain voltage in an n- MOSFET is | (c) | 775  $\Omega$ negative, it is operating in

- (a) Active region

- (b) Inactive region

- (c) Ohmic region

- (d) Reactive region

- 2. Consider the following statements regarding a differential amplifier using an FET pair, the differential output offset voltage is due to

- 1. Mismatch between FET parameters

- 2. Difference between the values of resistors used in the circuit even through they are marked nominally equal

- 3. Variation in the operating voltage of the circuit

Which of the above statements are correct?

### **IEE ESE - 2014**

- (a) 1, 2 and 3

- (b) 2 and 3 only

- (c) 1 and 3 only

- (d) 1 and 2 only

- 3. Statement (I): MOSFET's are intrinsically faster than bipolar devices

Statement (II): MOSFETs have excess minority carrier

### [EE ESE - 2013]

- (a) Both statement(I) and statement (II) are individually true and statement (II) is the correct explanation of statement (I)

- (b) Both statement(I) and statement (II) are individually true but statement (II) is not the correct explanation of statement (I)

- (c) Statement (I) is true but statement (II) is false

- (d) Statement (I) is false but statement (II) is true

- The value of the capacity reactance obtainable from a reactance FET whose g<sub>m</sub> is 12 rms when the gate-to-source resistance is 1/9 of the reactance of the gate-to-drain capacitor at frequency 5MHz is

[EE ESE - 2013]

(a)  $650\Omega$

(b)  $750\Omega$

(d)  $800\Omega$

- [EE ESE 2015] 5. The following statements refer to an nchannel FET operated in the active region

- 1.The gate voltage V<sub>GS</sub> reverse biases the junction

- 2. The drain voltage V<sub>DD</sub> is negative with respect to the source

- 3. The current in the n channel is due to electrons

- 4. Increasing in the reverse bias V<sub>GS</sub> increase the cross section for conduction

### [EE ESE - 2013]

- (a) 1 and 2

- (b) 1 and 3

- (c) 2 and 3

- (d) 3 and 4

- 6. The regions of operation of MOSFET to work as a linear resistor and linear amplifier are

### [EE ESE - 2013]

- (a) Cut off and saturation respectively

- (b) Triode cut off respectively

- (c) Triode and saturation respectively

- (d) Saturation and triode respectively

- 7. Statement (I): Most JFETs are designed to work in depletion mode

Statement (II): Depletion mode takes advantage of very high input resistance of reverse biased state

### [EE ESE - 2012]

- (a) Both statement(I) and statement (II) are individually true and statement (II) is the correct explanation of statement (I)

- (b) Both statement(I) and statement (II) are individually true but statement (II) is not the correct explanation of statement (I)

- (c) Statement (I) is true but statement (II) is false

- (d) Statement (I) is false but statement (II) is true

## **About ECG Publications**

Engineers Career Group provides you a wide range of Printed Study Material designed specially for ESE, GATE & SSC-JE Preparation. Includes Mock Tests, Sample Papers, Previous Year Papers with Topic-Wise Solutions. Check it out today.

### **Our Technical & Non-Technical Books**

### ESE (4 STREAMS) | GATE (5 STREAMS) | SSC-JE (3 STREAMS)