# **GATE** 2019

# DIGITAL ELECTRONICS

# **ELECTRICAL ENGINEERING**

#### A Unit of ENGINEERS CAREER GROUP

Head O ce: S.C.O-121-122-123, 2<sup>nd</sup> oor, Sector-34/A, Chandigarh-160022

Website: www.engineerscareergroup.in Toll Free: 1800-270-4242

E-Mail: ecgpublica ons@gmail.com | info@engineerscareergroup.in

**GATE-2019:** Digital Electronics | Detailed theory with GATE & ESE previous year papers and detailed solu ons.

©Copyright @2016 by ECG Publica ons (A unit of ENGINEERS CAREER GROUP)

All rights are reserved to reproduce the copy of this book in the form storage, introduced into a retrieval system, electronic, mechanical, photocopying, recording, screenshot or any other form without any prior wri en permission from ECG Publica ons (A Unit of ENGINEERS CAREER GROUP).

First Edi on: 2016

Price of Book: INR 510/-

**ECG PUBLICATIONS** (A Unit of ENGINEERS CAREER GROUP) collected and proving data like: theory for di erent topics or previous year solu ons very carefully while publishing this book. If in any case inaccuracy or prin ng error may nd or occurred then **ECG PUBLICATIONS** (A Unit of ENGINEERS CAREER GROUP) owes no responsibility. The sugges ons for inaccuracies or prin ng error will always be welcome by us.

|    | CONTENTS                      |         |

|----|-------------------------------|---------|

|    | CHAPTER                       | PAGE    |

| 1. | NUMBER SYSTEM                 | 1-37    |

| 2. | LOGIC GATES & BOOLEAN ALGEBRA | 38-124  |

| 3. | COMBINATIONAL IC'S            | 125-179 |

| 4. | SEQUENTIAL LOGIC ANALYSIS     | 180-270 |

| 5. | DIGITAL TO ANALOG CONVERTER   | 271-311 |

| 6. | DIGITAL LOGIC FAMILIES        | 312-360 |

|    |                               |         |

### CHAPTER - 1 NUMBER SYSTEM

#### **1.1 DATA REPRESENTATION**

| Magnitude Representation                                                                                                                                                             | <b>Complement Representation</b>                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>1.Unsigned magnitude representation<br/>(positive): No sign bit</li> <li>2.Signed magnitude representation (positive,<br/>negative): One extra bit (sign) as MSB</li> </ul> | <ol> <li>(r–1)'s complement: (positive, negative)</li> <li>R's complement: (positive, negative)</li> <li>MSB = 0 (positive)</li> <li>MSB = 1 (negative)</li> </ol> |  |

#### 1.1.1 Sign Magnitude Representation

"+" sign before a number indicate that it is positive (+ve) number and negative (-ve) sign before a number indicate that it is -ve number.

Replace +ve = 0 (MSB); -ve = 1 (MSB) Example.  $(+1100101)_2 \rightarrow (01100101)_2$   $(+101.001)_2 \rightarrow (0101.001)_2$   $(-10010)_2 \rightarrow (110010)_2$  $(-110.101)_2 \rightarrow (1110.101)_2$

**1.1.2 Signed Representation** Ranges is identical as that of 1's complement is also has 2 unique representation for zero Range =  $-(2^{n-1}-1)$  to  $+(2^{n-1}-1)$ (n = 7): (-63) to (+63)

#### 1.1.3 Complement

There are two type of complements: 1. (r-1)'s complement 2. (r)'s complement Where, r is base of complement

Binary (r = 2)

$$2^{\circ}s$$

Octal (r = 8)  $7^{\circ}s$

8  $8^{\circ}s$

Hexadecimal (r = 16)

Decimal (r =10)  $-\frac{9^{3}s}{10^{3}}$

(r-1)'s complements: To determine the complement subtract the given no form maximum number possible in base.

1. The number of bytes required to represent the BCP code 100010011001 corresponds to the decimal number 1856357 in packed BCD following number in base -5 systems (Binary Coded Decimal) from is [GATE - 2006] [GATE - 2014] (a) 423 (b) 1324 (c) 2201 (d) 4231 2. Which of the following is an invalid state in an 8-4-2-1 Binary coded decimal counter 7. Decimal 43 in Hexadecimal and BCD [GATE - 2014] number system is respectively (a) 1000(b) 1 0 0 1 [GATE - 2005] (c) 0 0 1 1 (d) 1 1 0 0 (a) B2, 0100 0011 (b) 2B, 0100 0011 (c) 2B, 0011 0100 (d) B2, 0100 0100 3. The two numbers represented in signed 2's complement form are P=11101101 and 8. The range of signed decimal numbers that Q=11100110. If Q is subtracted from P, the can be represented by 6-bite 1's complement value obtained in signed 2's complement form number is is [GATE - 2004] [GATE - 2008] (a) -31 to +31(b) -63 to +64(a) 100000111 (b) 00000111 (c) -64 to +63(d) -32 to +31(d) 111111001 (c) 11111001 9. 11001, 1001 and 111001 correspond to the **4.** X=01110 and Y=11001 are two 5-bit binary 2's complement representation of which one of numbers represent in two's complement format. the following sets of number? The sum of X and Y represented in two's [GATE - 2004] complement format using 6 bit is : (a) 25, 9 and 57 respectively [GATE - 2007] (b) -6, -6 and -6 respectively (b) 001000 (a) 100111 (c) -7, -7 and -7 respectively (c) 000111 (d) 101001 (d) -25, -9 and -57 respectively 5. The Octal equivalent of HEX and number 10. -bit 2's complement representation of a AB.CD is decimal number is 1000. The number is [GATE - 2007] [GATE - 2002] (a) 253.314 (b) 253.632 (a) + 8(b) 0(c) 526.314 (d) 526.632 (c) - 7(d) - 86. A new Binary Coded Pentary (BCP) number **11.** The 2's complement representation of -17 is system is proposed in which every digit of a [GATE - 2001] number is represented base-5 by its (a) 01110 (b) 01111 corresponding 3-bit binary code. For example (c) 11110 (d) 10001 the base-5 number 24 will be represented by its BCP code 010100. In the numbering system the

#### DIGITAL ELECTRONICS

# CHAPTER - 2 LOGIC GATES & BOOLEAN ALGEBRA

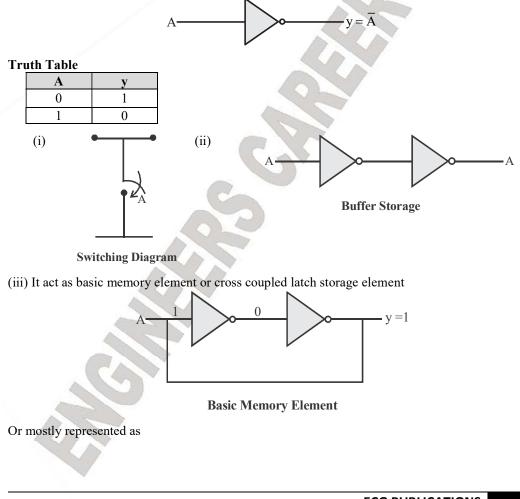

#### 2.1 LOGIC GATE

1. The fundamental building block of digital system. Logic gate means that output and input pattern of gate are assigned logically.

2. The inter connection of Gate to perform a variety of logical operation is called logic design. 3. The input and output of logic gate can occur only in two levels. These level are termed as high (1) and Low (0) simply.

4.Truth table show how the logic circuit o/p respond to various combination of logic level of i/p. There are various types of gates:

(i)Basic Gates: NOT, AND & OR

(ii)Universal Gate: NAND & NOR

(iii)EXOR & ENOR: Arithmetic, comparator, code converter, parity generator and parity checker.

#### 1. NOT Gate

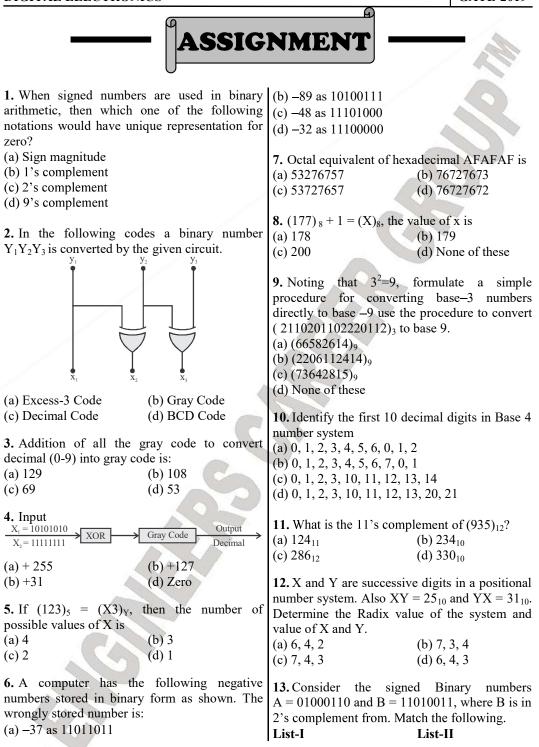

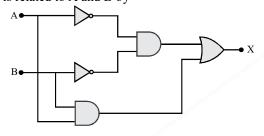

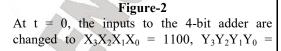

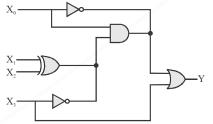

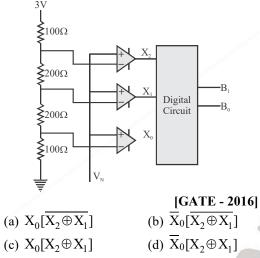

**1.** A and B are the logical inputs and X is the 0100 and  $Z_0 = 1$ . The output of the ripple carry logical output shown in the figure. The output X adder will be stable at t (in ns) = is related to A and B by

[GATE - 2017] (b)  $X = AB + \overline{B}A$ (a)  $X = \overline{A}B + \overline{B}A$ (c)  $X = AB + \overline{AB}$ (d)  $X = \overline{A}\overline{B} + \overline{B}A$

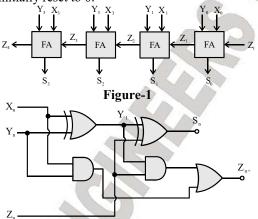

2. Figure 1 shows a 4-bit ripple carry adder realized using full adders and figure 2 shows the circuit of a full adder (FA). The propagation delay of the XOR, AND and OR gates in figure 2 are 20ns, 15ns and 10 ns, respectively. Assume all the inputs to the 4-bit adder are initially reset to 0.

[GATE - 2017]

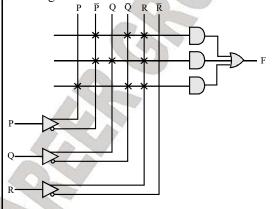

3. A programmable logic array (PLA) is shown in the figure.

The Boolean function F implemented is

$$[GATE - 2017]$$

(a)  $\overline{PQR} + \overline{PQR} + \overline{PQR}$

(b)  $(\overline{P} + \overline{Q} + R)(\overline{P} + Q + R + (P + \overline{Q} + \overline{R})$

(c)  $\overline{PQR} + \overline{PQR} + \overline{PQR}$

(d)  $(\overline{P} + \overline{Q} + R)(\overline{P} + Q + R) + (P + \overline{Q} + \overline{R})$

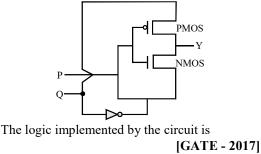

4. For the circuit shown in figure, P and Q are the inputs and Y is the output.

#### DIGITAL ELECTRONICS

GATE-2019

# CHAPTER - 3 COMBINATIONAL IC'S

#### **3.1 INTRODUCTION**

1.Gates are available as SSI's.

2.Adder, Multiplexer, Comparators and Encoder's are available in MSI.

3.SSI gates are mainly used for realizing simple Logic functions normally encountered in intercounting.

#### 3.1.1 Sequential logic

Logic circuits whose output are determined by the sequence in which input signals are applied

#### 3.1.2 Glitch

A momentry (short pulse) Duration pulse.

For any logic Design it is always essential to design a product which meets the requirement as:

- 1. Minimum cost

- 2. Minimum space requirement

- 3. Maximum speed of operation

- 4. Easy availability of component

- 5. Ease of inter connection of component

- 6. Easy to Design

#### Example.

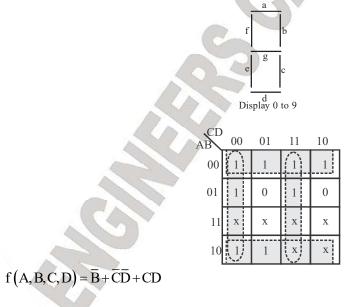

Basic Tool used in combinational circuit analysis is Karnaugh map (k-Map)

If we design this display by 4 bit then form (0 to 9) = BCD code valid and A to F (all status are invalid)

$f(A, B, C, D) = \sum (0, 1, 2, 3....9) + d \sum (10, 11, 12, 13, 14)$

1. The logic gates shown in the digital circuit below use strong pull-down nMOS transistors for LOW logic level at the outputs. When the pull-downs are off, high-value resistors set the output logic levels to HIGH (i.e. the pull-ups are weak). Note that some nodes are intentionally shorted to implement "wired logic". Such shorted nodes will be HIGH only if the outputs of all the gates whose outputs are shorted are HIGH.

The number of distinct values  $X_3 X_2 X_1 X_0$  (out of the 16 possible values) that give Y = 1 is

[GATE - 2018]

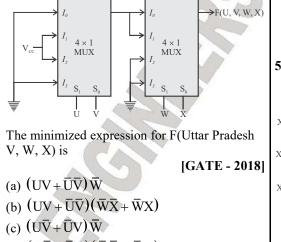

**2.** A four-variable Boolean function is realized using  $4 \times 1$  multiplexes as shown in the figure.

(d)  $(U\overline{V} + \overline{U}V)(\overline{W}\overline{X} + \overline{W}X)$

The logic gates shown in the digital circuit below use strong pull-down nMOS transistors for LOW logic level at the outputs. When the pull-downs are off, high-value resistors set the A and B is

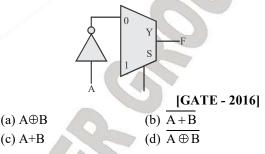

Consider the following circuit which uses a 2-to-1 multiplexer as shown in the figure below. The Boolean expression for output F in terms of A and B is

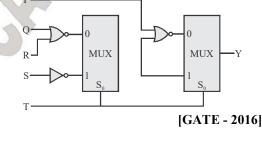

**4.** For the circuit shown in figure, the delays of NOR gates, multiplexer and inverters are 2ns, 1.5ns and 1ns, respectively. If all the inputs P,Q,R,S and T are applied at the same time instant, the maximum propagation delay (in ns) of the circuit is \_\_\_\_\_.

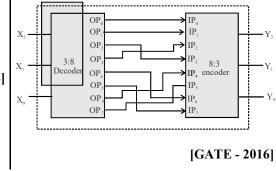

5. Identify the circuit below

ECG PUBLICATIONS A unit of ENGINEERS CAREER GROUP

# **CHAPTER - 4** SEQUENTIAL LOGIC ANALYSIS

#### **4.1 INTRODUCTION**

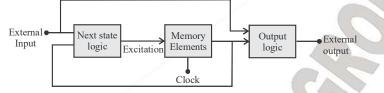

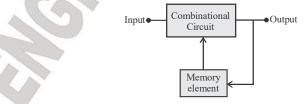

In combinational circuit the present o/p depend only upon the present input any prior level. (Input condition) does not have any effect on present output.

Next state depends upon next state logic and clock is used to receive & store data.

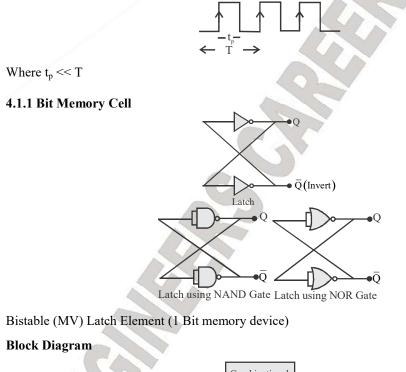

#### **Timing Diagram**

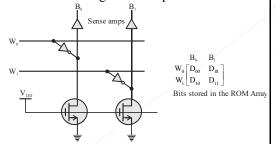

**1.** A 2 × 2 ROM array is built with the help of diodes as shown in the circuit below. Here  $W_0$  and  $W_1$  are signals that select the word lines and  $B_0$  and  $B_1$  are signals that are output of the sense amps based on the stored data corresponding to the bit lines during the read operation.

During the read operation, the selected word line goes high and the other word line is in a high impedance state. As per the

implementation shown in the circuit diagram above, what are the bits corresponding to  $D_{ij}$ (where I = 0 or 1 and j = 0 or 1) stored in the ROM?

$$[GATE - 2018]$$

$$(a) \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$$

$$(b) \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}$$

$$(c) \begin{bmatrix} 1 & 0 \\ 1 & 0 \end{bmatrix}$$

$$(d) \begin{bmatrix} 1 & 1 \\ 0 & 0 \end{bmatrix}$$

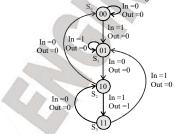

**2.** The state diagram of a finite state machine (FSM) designed to detect an overlapping sequence of three bits is shown in the figure. The FSM has an input 'In' and an output 'out'. The initial state of the FSM is  $S_0$ .

If the input sequence is 10101101001101, starting with the left most bit, then the number of times 'Out' will be 1 is

#### [GATE - 2017]

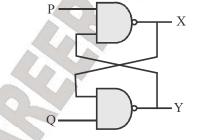

**3.** In the latch circuit shown, the NAND gates have non-zero, but unequal propagation delays. The present input condition is:  $P = Q = 0^{\circ}$ , if the input condition is changed simultaneously to  $P = Q = 1^{\circ}$ , the outputs X and Y are

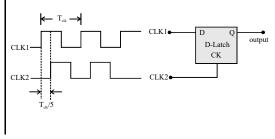

**4.** Consider the D-latch shown in the figure, which is transparent when its clock input CK is high and has zero propagation delay. In the figure, the clock signal CLK1 has a 50% duty cycle and CLK2 is a one-fifth period delayed version of CLK1. The duty cycle at the output of the latch in percentage is \_\_\_\_\_.

**ECG PUBLICATIONS** A unit of ENGINEERS CAREER GROUP

#### **DIGITAL ELECTRONICS**

## CHAPTER - 5 DIGITAL TO ANALOG CONVERTOR

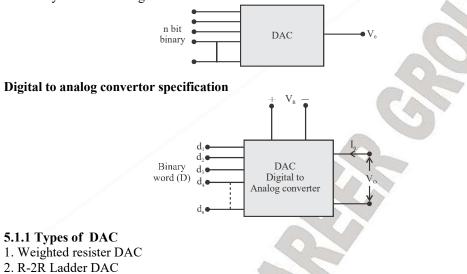

#### 5.1 DIGITAL TO ANALOG CONVERSION

1. It requires insulation of digital information to an equation analog information.

2. Usually refers as coding device.

#### 5.1.2 Parameter

- 1. Resolution

- 2. Analog output voltage

- 3. V<sub>Fs</sub>

- 4. % resolution

- 5. Error / accuracy

#### 5.1.3 General Equation

$V_0 = k \{ V_{Fs} \left( d_1 2^{-1} + d_2 2^{-2} + \dots + d_n 2^{-n} \right)$

Where,  $V_{FS}$  is full scale output voltage k is scaling factor usually "1".  $d_1$  is MSB with weight of  $V_{Fs}$  / 2

$d_n$  is LSB with weight of  $V_{Fs} / 2^n$

#### 1. Resolution (D to A converter)

(i)Resolution of DAC is change in analog voltage corresponding to 1 bit LSB increment.

Step size = Resolution =  $\frac{V_r}{2^n - 1}$

Where n is number of bit

v<sub>r</sub> is reference voltage corresponding to logic 1.

(ii) It is smallest change in analog output.

ECG PUBLICATIONS 271

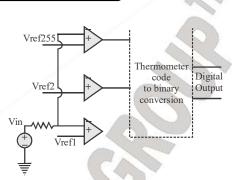

1. A 2-bit flash Analog to Digital Converter (ADC) is given below. The input is  $0 \le V_N \le 3$  Volts. The expression for the LSB of the output  $B_0$  as a Boolean function of  $X_2$ ,  $X_1$  and  $X_0$  is

2. In an N bit flash ADC, the analog voltage is fed simultaneously to  $2^{N}$  –1 comparators. The output of the comparators is then encoded to a binary format using digital circuit. Assume that the analog voltage source Vin (whose output is being converted to digital format) has a source resistance of 75 $\Omega$  as shown in the circuit diagram below and the input capacitance of each comparator is 8pF. The input must settle to an accuracy of ½ LSB even for a full scale input change for proper conversion. Assume that the time taken by the thermometer to binary encoder is negligible.

G

If the flash ADC has 8 bit resolution, which one of the following alternatives is closest to the maximum sampling rate?

#### [GATE - 2016]

- (a) 1 mega samples per second

- (b) 6 mega samples per second

- (c) 64 mega samples per second

- (d) 256 mega samples per second

**3.** Consider a four bit D to A convener. The analog value corresponding to digital signals of values 0000 and 0001 are 0 V and 0.0625 V respectively. The analog value (in Volts) corresponding to the digital signal 1111 is

#### [GATE - 2015]

**4.** Consider a four bit D to A convener the analog value corresponding to digital signals of values 0000 and 0001 are 0 V and 0.0625 V respectively. The analog value (in Volts) corresponding to the digital signal 1111 is

#### [GATE - 2015]

**5.** If WL is the Word Line and BL the Bit Line, an SRAM cell is shown in

298

# CHAPTER - 6 DIGITAL LOGIC FAMILIES

#### 6.1 INTRODUCTION

1.Basically there are two types of semiconductor devices such as bipolar, unipolar, and based on these devices; integrated circuit (digital) have been made which are commercially available.

2. Various digital functions are being fabricated in a variety of form by using bipolar and unipolar technologies.

3.A group of (compatible IC's) with the same logic level and supply voltage for performing various logic families have been fabricated using a specific circuit configuration which is referred as logic family.

4. The various parameter or characteristics of digital IC's used to compare their performances are:

(iv)Fan out

(ii)Power dissipation

(vi)Noise Immunity

(a) Schottky TTL

(viii)Power supply Requirement

(ii)Unsaturated/Non-saturated

(b) ECL(Emitter Coupled Logic)

(i)Speed of operation

(iii)Figure of Merit

(v)Current/voltage parameter (vii)Operating Temperature Range

(ix)Flexibilities Available

#### 6.2 THERE ARE TWO TYPES OF LOGIC FAMILIES

**1.Bipolar Logic Family**

(i) Saturated

(a) RTL(Resistor Transistor Logic)

(b) DCTL

(c) I<sup>2</sup>L

(d) DTL

(e) TTL

(f) HTL

#### 2. Unipolar Logic Family

(i) MOS: MOSFET are employed in MOS Logic

(a)NMOS

(b)PMOS

(c)CMOS(Complementary Metal Oxide Semiconductor)

(d)BiCMOS uses CMOS for input and logic operation and Bipolar Devices for output.

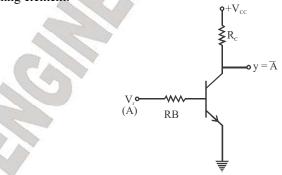

#### 6.3 BASIC CONCEPTS OF LOGIC FAMILIES ANALYSES

Basic switching element:

**ECG PUBLICATIONS** A unit of ENGINEERS CAREER GROUP

|                                                                                            |                                                                                           | 0                                                                                     |                                               |                                     |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------|

|                                                                                            | 1. Which has least po                                                                     | wer dissipation                                                                       | 7. In which                                   | of the following option, the logic  |

|                                                                                            | (a) TTL                                                                                   | (b) Schottky TTL                                                                      |                                               | arranged in the decreasing order of |

|                                                                                            | (c) CEL                                                                                   | (d) CMOS                                                                              | Power dissip                                  |                                     |

|                                                                                            |                                                                                           |                                                                                       | (a) TTL, DT                                   |                                     |

|                                                                                            | 2. The TTL open coll                                                                      | ector output of two 2-input                                                           | (b) CMOS, 7                                   |                                     |

|                                                                                            |                                                                                           | nected to a common pull-                                                              |                                               |                                     |

|                                                                                            | up resistor. If the inputs of the gates are A, B, C                                       |                                                                                       | (d) DTL, CMOS, TTL                            |                                     |

|                                                                                            |                                                                                           | y. The output is equal to                                                             |                                               |                                     |

|                                                                                            | (a) $\overline{\mathbf{A} \cdot \mathbf{B}} \cdot \overline{\mathbf{C} \cdot \mathbf{D}}$ | (b) $\overline{\mathbf{A} \cdot \mathbf{B}} + \overline{\mathbf{C} \cdot \mathbf{D}}$ |                                               | ard TTL, totem pole refers to       |

|                                                                                            |                                                                                           |                                                                                       | (a) Multi em                                  |                                     |

|                                                                                            | (c) $\mathbf{A} \cdot \mathbf{B} + \mathbf{C} \cdot \mathbf{D}$                           | (d) $A \cdot B \cdot C \cdot D$                                                       | (b) The phase                                 |                                     |

|                                                                                            |                                                                                           |                                                                                       | (c) CMOS, 7                                   |                                     |

|                                                                                            |                                                                                           | D gates is used to be as an                                                           |                                               |                                     |

|                                                                                            |                                                                                           | e following measures will                                                             |                                               |                                     |

| achieve better results?<br>(a)The two inputs not used are kept open                        |                                                                                           |                                                                                       | 9. In a standard TTL, totem pole refers to    |                                     |

|                                                                                            |                                                                                           |                                                                                       | (a) Multi emitter stage                       |                                     |

|                                                                                            |                                                                                           | ot used are connected to                                                              |                                               |                                     |

|                                                                                            | ground (0 level)                                                                          |                                                                                       | (c) The output buffer                         |                                     |

|                                                                                            |                                                                                           | ot used are (connected to                                                             | (d) Open collector output stage               |                                     |

|                                                                                            | supply $V_{DD}$ (1 level)                                                                 |                                                                                       | <b>10.</b> In TTL floating input to a gate is |                                     |

|                                                                                            | (d)None of the above                                                                      |                                                                                       | considered                                    |                                     |

|                                                                                            |                                                                                           |                                                                                       | (a) Logical (                                 | )                                   |

|                                                                                            | · · · · ·                                                                                 | $fmA, I_{IL}(max) = 0.0016A,$                                                         | (b) Logical 1                                 |                                     |

|                                                                                            | find out                                                                                  | (1) 10                                                                                | (c) Either 0 or 1                             |                                     |

|                                                                                            | (a) 16                                                                                    | (b) 10<br>(1) 100                                                                     |                                               | will be undefined                   |

|                                                                                            | (c) 1.6                                                                                   | (d) 100                                                                               | (u) Guie 0/1                                  | will be undefined                   |

|                                                                                            | 5 The basic sets of E                                                                     | CL family is                                                                          | 11. The figu                                  | are of merit of a logic is given by |

|                                                                                            | 5. The basic gate of E (a) NAND                                                           | (b) NOR                                                                               | (a)Gain bandwidth product                     |                                     |

|                                                                                            | (c) XOR                                                                                   | (d) AND                                                                               | (b)Propagati                                  | on delay and power dissipation      |

|                                                                                            | (U) AUK                                                                                   |                                                                                       | product                                       | +                                   |

|                                                                                            | 6. Which one of the following logic functions is                                          |                                                                                       |                                               |                                     |

|                                                                                            |                                                                                           |                                                                                       | (d)Noise margin and power dissipation product |                                     |

| implemented by the gates when their open collector type outputs are tied together as shown |                                                                                           |                                                                                       | 12 14 1                                       |                                     |

|                                                                                            | in the given figure?                                                                      |                                                                                       | 12. Match list-I with list-II and select the  |                                     |

|                                                                                            |                                                                                           |                                                                                       | correct answer using the code given below in  |                                     |

|                                                                                            |                                                                                           |                                                                                       | the list                                      | I tot II                            |

|                                                                                            |                                                                                           |                                                                                       | List-I                                        | List-II<br>(i)High for out          |

|                                                                                            |                                                                                           |                                                                                       | A. HTL<br>P. CMOS                             | (i)High fan out                     |

|                                                                                            |                                                                                           | )                                                                                     | B. CMOS<br>C. I <sup>2</sup> L                | (ii)Highest speed of operation      |

|                                                                                            |                                                                                           |                                                                                       | D. ECL                                        | (iii)High noise immunity            |

|                                                                                            | (a) $F = AB + C + D$                                                                      | (b) $F = \overline{AB(C+D)}$                                                          | D. ECL                                        | (iv)Lowest product of power and     |

|                                                                                            |                                                                                           |                                                                                       |                                               | delay                               |

|                                                                                            | (c) $F = AB + (C + D)$                                                                    | (d) $F = AB + C + D$                                                                  | Coder                                         |                                     |

|                                                                                            |                                                                                           |                                                                                       | Codes:                                        |                                     |

|                                                                                            |                                                                                           |                                                                                       |                                               |                                     |